# Conference Program

Sheraton La Jolla Hotel, La Jolla, California, USA

#### **Message from the General Chairs**

On behalf of the Organizing Committee, it is our pleasure to welcome you to the 2014 ACM/IEEE International Symposium on Low Power Electronics and Design (ISLPED 2014), which is held in La Jolla, California, on August 11-13, 2014. La Jolla in Spanish means "The Jewel". It is the Jewel of America's finest city, San Diego. La Jolla is located 15 minutes from downtown San Diego. It features shimmering ocean views to timeless landmarks. It is home to renowned institutions, such as the Scripps Institution of Oceanography, the Stephen Birch Aquarium & Museum, and the University of California, San Diego.

ISLPED (<a href="www.islped.org">www.islped.org</a>) is the premier forum for presentation of recent advances in all aspects of low-power design and technologies, ranging from process and circuit technologies, simulation and synthesis tools, to system-level design and software optimization. This year we have kept up the tradition of having outstanding contributions from the low-power design community. The Technical Program Chairs, Muhammad Khellah (Intel) and Renu Mehra (Synopsys), have worked hard to put together an excellent Technical Program. Many thanks go to the Technical Program Committee comprising of leading researchers in the area of low-power design and to Professors Mingoo Seok and Yiran Chen, for chairing the Low-Power Design Contest.

The ISLPED 2014 Organizing Committee has been working tirelessly to bring you a world-class conference experience: Xiangyu Dong and Jack Sampson, Local Arrangements Chairs; Eren Kursun, Industrial Liaison; Yu Wang, Treasurer and Registration Chair; Theo Theocharides, Web Chair; and Deming Chen, Baris Taskin, Jose Ayala, Publicity Chairs. We are also grateful to the Executive Committee, chaired by Massoud Pedram, for their continued guidance in making ISLPED 2014 a great success.

ISLPED 2014 has been fortunate to receive strong support from the industry. In particular, we appreciate the generous financial support from Intel, Synopsys, Qualcomm, IBM, Huawei, and Microsoft for ISLPED 2014. ISLPED 2014 is sponsored by ACM, ACM-SIGDA, IEEE, and IEEE-CAS, with technical support from the SSCS and EDS. We hope that you will enjoy the excellent ISLPED 2014 program this year, and have a pleasant, enriching and memorable experience at La Jolla.

Tanay Karnik, Intel ISLPED '14 General Co-Chair

#### **Message from the Program Chairs**

It is our great pleasure to welcome you to the 2014 ACM/IEEE International Symposium on Low Power Electronics and Design – ISLPED'14, in the beautiful city of La Jolla, CA, USA. The mission of our symposium is to provide education and technical enrichment for professionals and promote advancement of the state-of-the-art in the area of low power electronics and design.

This year, the call for papers attracted 184 submissions from Asia, Africa, Europe, and North & South America. The Technical Program Committee (TPC) accepted a total of 63 papers with 43 full-length presentations and 20 posters. The accepted papers cover a variety of low-power topics in technologies, circuits, logic & architecture, CAD Tools & methodologies, systems & platforms, and software and applications. We are very thankful to the authors for their contributions and to our TPC members for volunteering their valuable time and effort in reviewing the papers, and providing feedback to the authors. In addition to the above accepted papers, this year's program features:

- Three Keynote Speeches by Dr. Karim Arabi, Qualcomm; Prof. Jason Cong, UCLA, and Dr. Partha Ranganathan, Google

- Industry Focus Session on Low-power Circuits & Technologies

- Four Embedded Invited Papers on Emerging Low-power Topics

- Embedded Tutorial by industry EDA experts

We hope the above talks will complement our main program by providing you with an in-depth understanding of the low-power state-of-the-art as well as gives you valuable insights into future trends.

Finally, we hope that you will find the overall program interesting and thoughtprovoking and that the symposium will provide you with a valuable opportunity to share ideas with other researchers and practitioners from institutions around the world.

Renu Mehra, Synopsys ISLPED '14 Program Co-Chair

Muhammad M. Khellah, Intel

# **Program at a Glance: Monday**

| 8:30-8:45   | Welcome Address: University Room                                             |                                                                                |

|-------------|------------------------------------------------------------------------------|--------------------------------------------------------------------------------|

|             | Keynote 1: University Room                                                   |                                                                                |

| 8:45-9:45   | Low power Design Techniques In Mobile Processors  Karim Arabi, Qualcomm      |                                                                                |

|             | Session 1A: University Room                                                  | Session 1B: Executive Room                                                     |

| 10:15-11:55 | Photonics, Spintronics,<br>Approximate Computing and<br>Front-End Throttling | Approximate Computing and<br>Quality Driven Power-Aware<br>System Design       |

| 11:55-1:30  | Posters: Co                                                                  | oast Ballroom                                                                  |

| 11:55-1:30  | Lunch: Coast Ballroom                                                        |                                                                                |

|             | Session 2A: University Room                                                  | Session 2B: Executive Room                                                     |

| 1:30-2:45   | Emerging Technologies                                                        | Energy-Efficient Systems Using<br>Emerging Non-volatile Memory<br>Technologies |

| 2:45-3:15   | Ві                                                                           | reak                                                                           |

|             | Session 3A: University Room                                                  | Session 3B: Executive Room                                                     |

| 3:15-4:30   | Clock and IO Circuit<br>Techniques                                           | Thermal-Aware Design: from<br>Device to System                                 |

| 4:30-4:45   | Break                                                                        |                                                                                |

| 4.45.6.00   | Session 4A: University Room                                                  | Session 4B: Executive Room                                                     |

| 4:45-6:00   | Industry Special Session                                                     | Embedded Tutorial                                                              |

| 6:00 - 8:00 | Industry reception: Coast Ballroom                                           |                                                                                |

### **Program at a Glance: Tuesday**

|             | Keynote 2: U                                                                            | niversity Room                                                      |

|-------------|-----------------------------------------------------------------------------------------|---------------------------------------------------------------------|

| 8:45-9:45   | Accelerator-Rich Architectures – from Single-chip to Datacenters,  Jason Cong, UCLA     |                                                                     |

| 9:30-10:00  | Bi                                                                                      | reak                                                                |

|             | Session 5A: University Room                                                             | Session 5B: Executive Room                                          |

| 10:00-11:40 | GPU Voltage Noise, Uncore<br>Power Modeling, Memory<br>Power Management, and<br>Testing | CAD for Low Power and<br>Reliability                                |

| 11:40-12:20 | Posters: Co                                                                             | past Ballroom                                                       |

| 12:20-1:30  | Lunch: Coa                                                                              | ast Ballroom                                                        |

|             | Session 6A: University Room                                                             | Session 6B: Executive Room                                          |

| 1:30-2:45   | Energy Efficient Digital Circuit<br>Techniques                                          | Optimizing Computation and<br>Communication in Mobile<br>Systems    |

| 2:45-3:15   | Ві                                                                                      | reak                                                                |

|             | Session 7A: University Room                                                             | Session 7B: Executive Room                                          |

| 3:15-4:30   | Voltage Reference and Power<br>Converter Circuits                                       | Variation and Reliability<br>Consideration for Low-Power<br>Systems |

| 4:30-4:45   | Break                                                                                   |                                                                     |

| 4.4E 6.00   | Session 8A: University Room                                                             | Session 8B: Executive Room                                          |

| 4:45-6:00   | Design Contest                                                                          | Poster Presentations                                                |

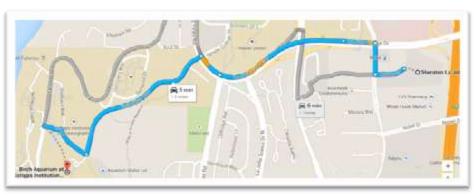

| 6:00 - 9:00 | Dinner + Banquet: Birch Aquarium                                                        |                                                                     |

#### **Program at a Glance: Wednesday**

|             | Keynote 3: U                                                                                         | niversity Room                                       |

|-------------|------------------------------------------------------------------------------------------------------|------------------------------------------------------|

| 8:30 - 9:30 | The New (System) Balance of Power and Opportunities for<br>Optimizations, Partha Ranganathan, Google |                                                      |

| 9:30-10:00  | Break                                                                                                |                                                      |

| 10:00-11:40 | Session 9A: University Room                                                                          | Session 9B: Executive Room                           |

|             | Energy Efficient Cache and<br>Memory Design                                                          | Energy Harvesting and Energy-<br>Aware System Design |

| 11:40-12:00 | Break                                                                                                |                                                      |

| 8:30-8:45   | Welcome Address: University Room                                                                                                                                          |                                                                                                                                                                                                                                                                                                              |

|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|             | Keynote 1: University Room                                                                                                                                                |                                                                                                                                                                                                                                                                                                              |

| 8:45-9:45   | Low power Design Techniques In Mobile Processors  Karim Arabi, VP of Engineering for Qualcomm Research  Session Chair: Yuan Xie (University of California, Santa Barbara) |                                                                                                                                                                                                                                                                                                              |

|             | Session 1A: University Room                                                                                                                                               | Session 1B: Executive Room                                                                                                                                                                                                                                                                                   |

| 10:15-11:55 | Photonics, Spintronics, Approximate Computing and Front-End Throttling                                                                                                    | Approximate Computing and<br>Quality Driven Power-Aware<br>System Design                                                                                                                                                                                                                                     |

|             | Session Chairs: Hans Jacobson<br>(IBM) and Umit Ogras (Arizona<br>State University)                                                                                       | Session Chairs: Xiangyu Dong<br>(Qualcomm) and Vivek Joy (Intel)                                                                                                                                                                                                                                             |

| 10:15-10:40 | EcoLaser: An Adaptive Laser<br>Control for Energy Efficient On-<br>Chip Photonic Interconnects<br>Yigit Demir, Nikos Hardavellas<br>Northwestern University               | (Best Paper Nominee) AxNN: Energy Efficient Neuromorphic Systems using Approximate Computing  Swagath Venkataramani; Ashish Ranjan; Kaushik Roy; Anand Raghunathan Purdue University                                                                                                                         |

| 10:40-11:05 | A Model for Array-based Approximate Arithmetic Computing with Application to Multiplier and Squarer Design  Botang Shao, Peng Li Texas A&M University                     | TONE: Adaptive Temperature Optimization for the Next Generation Video Encoders  Daniel Palomino <sup>1</sup> ; Muhammad Shafique <sup>2</sup> ; Altamiro Susin <sup>1</sup> ; Joerg Henkel <sup>2</sup> <sup>1</sup> Federal University of Rio Grande do Sul; <sup>2</sup> Karlsruhe Institute of Technology |

| 11:05-11:30                        | SPINDLE: SPIntronic Deep Learning Engine for Large-scale Neuromorphic Computing  Shankar Ganesh Ramasubramanian; Rangharajan Venkatesan; Mrigank Sharad; Kaushik Roy; Anand Raghunathan Purdue University | StoRM: Stochastic Recognition and Mining Processor  Vinay Chippa; Swagath Venkataramani; Kaushik Roy; Anand Raghunathan Purdue University                                                                                                                                                                                                                                                                                                                                                                                        |

|------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 11:30-11:55                        | Adaptive Front-End Throttling<br>for Superscalar Processors  Wei Zhang; Hang Zhang; John<br>Lach University of Virginia                                                                                   | Approximate Compressed Sensing: Ultra-Low Power Biosignal Processing via Aggressive Voltage Scaling on a Hybrid Memory Multi- core Processor  Daniele Bortolotti <sup>1</sup> ; Hossein Mamaghanian <sup>2</sup> ; Andrea Bartolini <sup>1</sup> ; Maryam Ashouei <sup>3</sup> ; Jan Stuijt <sup>3</sup> ; Pierre Vandergheynst <sup>2</sup> ; Luca Benini <sup>1</sup> ; David Atienza <sup>2</sup> <sup>1</sup> University of Bologna; <sup>2</sup> École polytechnique fédérale de Lausanne; <sup>3</sup> IMEC / Holst Center |

| 11:55-1:30 Posters: Coast Ballroom |                                                                                                                                                                                                           | oast Ballroom                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                                    | Lunch: Co                                                                                                                                                                                                 | past Ballroom                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|           | Session 2A: University Room                                                                                                                                                                                                                                                                               | Session 2B: Executive Room                                                                                                                                                                                                     |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1:30-2:45 | Emerging Technologies  Session Chairs: Arijit Raychowdhury (Georgia Institute                                                                                                                                                                                                                             | Energy-Efficient Systems Using<br>Emerging Non-Volatile Memory<br>Technologies                                                                                                                                                 |

|           | of Technology) and Patrick<br>Mercier (University of California,<br>San Diego)                                                                                                                                                                                                                            | Session Chairs: Vijay Raghunathan<br>(Purdue University) and Zhenyu Sun<br>(Broadcom)                                                                                                                                          |

|           | (Best Paper) An On-chip Autonomous Thermoelectric Energy Management System for Energy-Efficient Active Cooling                                                                                                                                                                                            | Making B+-Tree Efficient in PCM-Based Main Memory  Ping Chi; Wang-Chien Lee; Yuan Xie                                                                                                                                          |

| 1:30-1:55 | Borislav Alexandrov; Khondker Z.<br>Ahmed; Saibal Mukhopadhyay<br>Georgia Institute of Technology                                                                                                                                                                                                         | Pennsylvania State University                                                                                                                                                                                                  |

|           | Tunnel FET-Based Ultra-Low<br>Power, Low-Noise Amplifier<br>Design for Bio-signal Acquisition                                                                                                                                                                                                             | Sleep-Aware Variable Partitioning<br>for Energy-Efficient Hybrid PRAM<br>and DRAM Main Memory                                                                                                                                  |

| 1:55-2:20 | Huichu Liu <sup>1</sup> ; Mahsa Shoaran <sup>2</sup> ;<br>Xueqing Li <sup>1</sup> ; Suman Datta <sup>1</sup> ;<br>Alexandre Schmid <sup>2</sup> ;<br>Vijaykrishnan Narayanan <sup>1</sup><br><sup>1</sup> Pennsylvania State University;<br><sup>2</sup> Swiss Federal Institute of<br>Technology (EPFL); | Chenchen Fu <sup>1</sup> ; Mengying Zhao <sup>1</sup> ;<br>Chun Jason Xue <sup>1</sup> ; Alex Orailoglu <sup>2</sup><br><sup>1</sup> City University of Hong Kong;<br><sup>2</sup> University of California                    |

|           | (Invited paper) Performance Modeling for Emerging Interconnect Technologies in CMOS and Beyond-CMOS                                                                                                                                                                                                       | DR. Swap: Energy-Efficient Paging for Smartphones  Kan Zhong <sup>1</sup> ; Xiao Zhu <sup>1</sup> ; Tianzheng                                                                                                                  |

| 2:20-245  | Circuits  Sou-Chi Chang, Rouhollah M. Iraei, Vachan Kumar, Ahmet Ceyhan, and Azad Naeemi Georgia Tech University.                                                                                                                                                                                         | Wang <sup>2</sup> ; Dan Zhang <sup>1</sup> ; Xianlu Luo <sup>1</sup> ;<br>Duo Liu <sup>1</sup> ; Weichen Liu <sup>1</sup> ; Edwin Sha <sup>1</sup><br><sup>1</sup> Chongqing University; <sup>2</sup> University of<br>Toronto |

| 2:45-3:15 | В                                                                                                                                                                                                                                                                                                         | Break                                                                                                                                                                                                                          |

|           | Session 3A: University Room                                                                                                                                                                                                                                                                                                                | Session 3B: Executive Room                                                                                                                                                                                                                                                |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3:15-4:30 | Clock and IO Circuit Techniques                                                                                                                                                                                                                                                                                                            | Thermal-Aware Design: from Device to System                                                                                                                                                                                                                               |

| 3:15-4:30 | Session Chairs: Gordon Gammie<br>(MediaTek) and Jie Gu<br>(Maxlinear)                                                                                                                                                                                                                                                                      | Session Chairs: Jiang Hu (Texas A&M<br>University) and Umit Ogras (Arizona<br>State University)                                                                                                                                                                           |

| 3:15-3:40 | Quasi-Resonant Clocking: A<br>Run-time Control Approach for<br>True Voltage-Frequency-<br>Scalability                                                                                                                                                                                                                                      | Dynamic Thermal Management for FinFET-Based Circuits Exploiting the Temperature Effect Inversion Phenomenon                                                                                                                                                               |

| 3.13-3.40 | Visvesh Sathe<br>University of Washington                                                                                                                                                                                                                                                                                                  | Woojoo Lee; Yanzhi Wang; Tiansong<br>Cui; Shahin Nazarian; Massoud<br>Pedram<br>University of Southern California                                                                                                                                                         |

| 3:40-4:05 | An Energy-efficient 2.5D Through-silicon Interposer I/O with Self-adaptive Adjustment of Output-voltage Swing  Dongjun Xu <sup>1</sup> ; Sai Manoj P D <sup>1</sup> ; Hantao Huang <sup>1</sup> ; Ningmei Yu <sup>2</sup> ; Hao Yu <sup>1</sup> <sup>1</sup> Nanyang Technological University; <sup>2</sup> Xian University of Technology; | Buffered Clock Tree Synthesis Considering Self-Heating Effects  Chung-Wei Lin <sup>1</sup> ; Tzu-Hsuan Hsu <sup>2</sup> ; Xin-Wei Shih <sup>2</sup> ; Yao-Wen Chang <sup>2</sup> <sup>1</sup> University of California, Berkeley; <sup>2</sup> National Taiwan University |

| 4:05-4:30 | Reconfigurable Regenerator-<br>based Interconnect Design for<br>Ultra-Dynamic-Voltage-Scaling<br>Systems  Seongjong Kim; Mingoo Seok<br>Columbia University                                                                                                                                                                                | Therminator: A Thermal Simulator for Smartphones Producing Accurate Chip and Skin Temperature Maps  Qing Xie; Mohammad Javad Dousti; Massoud Pedram University of Southern California                                                                                     |

| 4:30-4:45 | E                                                                                                                                                                                                                                                                                                                                          | Break                                                                                                                                                                                                                                                                     |

|             | Session 4A: University Room                                                                                                                         | Session 4B: Executive Room                                                                                                                                                                           |

|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4:45-6:00   | Industry Special Session                                                                                                                            | Embedded Tutorial                                                                                                                                                                                    |

| 4.43-0.00   | Session Chair: Muhammad<br>Khellah (Intel)                                                                                                          | Session Chairs: Massimo Poncino<br>(Politecnico di Torino) and Renu<br>Mehra (Synopsys)                                                                                                              |

| 4:45-5:10   | (Invited Paper) Challenges in<br>Low-Power Analog Integrated<br>Circuit Design for Sub-28nm<br>CMOS Technologies<br>Amr Fahim<br>Semtech Corp.      | (Embedded Tutorial) Failing to Fail - Achieving Success in Advanced Low Power Design using UPF  Rick Koster <sup>1</sup> , Shreedhar Ramachandra <sup>2</sup> , Sushma Honnavara Prasad <sup>3</sup> |

| 5:10-5:35   | (Invited paper) Process and design solutions for exploiting FD-SOI technology towards energy efficient SOCs  Philippe Flatresse ST Microelectronics | <sup>1</sup> Mentor Graphics; <sup>2</sup> Synopsys Inc.;<br><sup>3</sup> Broadcom Corp                                                                                                              |

| 5:35-6:00   | (Invited paper) Embedded STT-MRAM for Emerging Mobile Applications: Toward Unified eNVM Solution  Kangho Lee, Seung H. Kang Qualcomm                |                                                                                                                                                                                                      |

| 6:00 - 8:00 | Industry reception: Coast Ballroom                                                                                                                  |                                                                                                                                                                                                      |

|             | Keynote 2: l                                                                                                                                                                                                                                                                                                                  | University Room                                                                                                                                                                                                                                                              |

|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 8:45-9:45   | Accelerator-Rich Architectures – from Single-Chip to Datacenters  Jason Cong, University of California, Los Angeles  Session Chair: Tanay Karnik (Intel)                                                                                                                                                                      |                                                                                                                                                                                                                                                                              |

| 9:30-10:00  | E                                                                                                                                                                                                                                                                                                                             | Break                                                                                                                                                                                                                                                                        |

|             | Session 5A: University Room                                                                                                                                                                                                                                                                                                   | Session 5B: Executive Room                                                                                                                                                                                                                                                   |

| 10:00-11:40 | GPU Voltage Noise, Uncore<br>Power Modeling, Memory<br>Power Management, and<br>Testing                                                                                                                                                                                                                                       | CAD for Low Power and Reliability  Session Chairs: Zhiru Zhang (Cornell                                                                                                                                                                                                      |

|             | Session Chairs: John Sampson<br>(Penn State University) and<br>Yaojun Zhang (Qualcomm)                                                                                                                                                                                                                                        | University) and Yiran Chen<br>(University of Pittsburgh)                                                                                                                                                                                                                     |

| 10:00-10:25 | (Best Paper Nominee) GPUVolt: Modeling and Characterizing Voltage Noise in GPU Architectures  Jingwen Leng <sup>1</sup> , Yazhou Zu <sup>1</sup> , Minsoo Rhu <sup>1</sup> , Meeta Sharma Gupta <sup>2</sup> and Vijay Janapa Reddi <sup>1</sup> <sup>1</sup> The University of Texas at Austin; <sup>2</sup> IBM T.J. Watson | Algorithms for Power-Efficient QoS in Application-Specific NoCs  Hao He, Gongming Yang and Jiang Hu  Texas A&M University                                                                                                                                                    |

| 10:25-10:50 | Empirically Derived Abstractions in Uncore Power Modeling for a Server-Class Processor Chip  Hans Jacobson, Arun Joseph, Dharmesh Parikh, Pradip Bose and Alper Buyuktosunoglu IBM                                                                                                                                            | Design and CAD Methodologies for<br>Low Power Gate-level Monolithic<br>3D ICs  Shreepad Panth <sup>1</sup> , Kambiz Samadi <sup>2</sup> ,<br>Yang Du <sup>2</sup> and Sung Kyu Lim <sup>1</sup> <sup>1</sup> Georgia Institute of Technology; <sup>2</sup> Qualcomm Research |

| <b> </b>    | Lunch: Coast Ballroom                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                               |

|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 11:40-12:20 | Posters: Coast Ballroom                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                               |

| 11:15-11:40 | Software Canaries: Software-<br>based Path Delay Fault Testing<br>for Variation-aware Energy-<br>efficient Design  John Sartori <sup>1</sup> and Rakesh Kumar <sup>2</sup> <sup>1</sup> University of Minnesota; <sup>2</sup> University of Illinois at Urbana-<br>Champaign                                                                                                | (Invited Paper) Bridging High Performance and Low Power in the era of Heterogeneous Computing Ruchir Puri IBM                                                                                                                                                                 |

| 10:50-11:15 | Content-Driven Memory Pressure Balancing and Video Memory Power Management for Parallel High Efficiency Video Coding  Felipe Sampaio <sup>1</sup> , Muhammad Shafique <sup>2</sup> , Bruno Zatt <sup>1</sup> , Sergio Bampi <sup>1</sup> and Joerg Henkel <sup>2</sup> <sup>1</sup> Federal University of Rio Grande do Sul; <sup>2</sup> Karlsruhe Institute of Technology | Efficient NBTI Modeling Technique Considering Recovery Effects  Reef Eilers <sup>1</sup> , Malte Metzdorf <sup>1</sup> , Domenik Helms <sup>1</sup> and Wolfgang Nebel <sup>1,2</sup> <sup>1</sup> OFFIS Institute for Computer Science; <sup>2</sup> University of Oldenburg |

|           | Session 6A: University Room                                                       | Session 6B: Executive Room                                                                                      |

|-----------|-----------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|

|           | Energy Efficient Digital Circuit                                                  | Optimizing Computation and                                                                                      |

| 1:30-2:45 | Techniques                                                                        | Communication in Mobile Systems                                                                                 |

| 1.30 2.43 | Session Chairs: Rob Gilmore                                                       | Session Chairs: Sujit Dey (University                                                                           |

|           | (Qualcomm) and Joyce Kwong                                                        | of California, San Diego) and Yiran                                                                             |

|           | (TI)                                                                              | Chen (University of Pittsburgh)                                                                                 |

|           | CASA: Correlation-Aware Speculative Adders                                        | A case for leveraging 802.11p for<br>Direct Phone-to-Phone                                                      |

|           | Speculative Adders                                                                | Communications                                                                                                  |

|           | Gai Liu; Ye Tao; Mingxing Tan;                                                    |                                                                                                                 |

| 1:30-1:55 | Zhiru Zhang                                                                       | Pilsoon Choi <sup>1</sup> ; Jason Gao <sup>1</sup> ; Nadesh                                                     |

|           | Cornell University                                                                | Ramanathan <sup>2</sup> ; Mengda Mao <sup>2</sup> ;<br>Shipeng Xu <sup>2</sup> ; Chirn-Chye Boon <sup>2</sup> ; |

|           |                                                                                   | Suhaib Fahmy <sup>2</sup> ; Li-Shiuan Peh <sup>1</sup>                                                          |

|           |                                                                                   | <sup>1</sup> MIT; <sup>2</sup> NTU;                                                                             |

|           | Synergistic Circuit and System                                                    | (Invited Paper) Leakage Mitigation                                                                              |

|           | Design for Energy-Efficient and                                                   | Techniques in Smartphone SoCs"                                                                                  |

|           | Robust Domain Wall Caches                                                         |                                                                                                                 |

| 1:55-2:20 |                                                                                   | John Redmond                                                                                                    |

|           | Seyedhamidreza Motaman;                                                           | Broadcom Corporation                                                                                            |

|           | Anirudh Iyengar; Swaroop<br>Ghosh                                                 |                                                                                                                 |

|           | University of South Florida                                                       |                                                                                                                 |

|           | Timing Errors in LDPC Decoding                                                    |                                                                                                                 |

|           | Computations with Overscaled                                                      |                                                                                                                 |

|           | Supply Voltage                                                                    |                                                                                                                 |

| 2:20-2:45 | Behnam Sedighi <sup>1</sup> ; N. Prasanth                                         |                                                                                                                 |

|           | Anthapadmanabhan²; Dusan                                                          |                                                                                                                 |

|           | Suvakovic <sup>2</sup>                                                            |                                                                                                                 |

|           | <sup>1</sup> University of Notre Dame; <sup>2</sup> Bell<br>Labs, Alcatel-Lucent; |                                                                                                                 |

| 2:45-3:15 | E                                                                                 | Break                                                                                                           |

|           | Session 7A: University Room                                                                                                                                                                                                                                                           | Session 7B: Executive Room                                                                                                                                                                                                                                                                            |  |

|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 3:15-4:30 | Voltage Reference and Power<br>Converter Circuits<br>Session Chairs: Swaroop Ghosh<br>(University of Florida) and<br>Nilanjan Banerjee (Qualcomm)                                                                                                                                     | Variation and Reliability Consideration for Low-Power Systems Session Chairs: Eli Bozorgzadeh (University of California, Irvine) and Younghyun Kim (Purdue University)                                                                                                                                |  |

| 3:15-3:40 | 2.3 ppm/°C, 40 nW MOSFET-<br>Only Voltage Reference  Oscar Elisio Mattia; Hamilton<br>Klimach; Sergio Bampi<br>Federal University of Rio Grande<br>do Sul                                                                                                                             | Aging Mitigation of Power Supply-Connected Batteries  Jaemin Kim <sup>1</sup> ; Alma Proebstl <sup>2</sup> ; Samarjit Chakraborty <sup>2</sup> ; Naehyuck Chang <sup>1</sup> <sup>1</sup> Seoul National University; <sup>2</sup> TU Munich                                                           |  |

| 3:40-4:05 | A Bipolar ±40 mV Self-Starting Boost Converter with Transformer Reuse for Thermoelectric Energy Harvesting  Nachiket Desai; Yogesh Ramadass; Anantha Chandrakasan Massachusetts Institute of Technology                                                                               | Variation tolerant design of a vector processor for Recognition, Mining and Systhesis  Vivek Kozhikkottu <sup>1</sup> ; Swagath Venkataramani <sup>1</sup> ; Sujit Dey <sup>2</sup> ; Anand Raghunathan <sup>1</sup> <sup>1</sup> Purdue University; <sup>2</sup> University of California, San Diego |  |

| 4:05-4:30 | Impact of Process Variation in Inductive Integrated Voltage Regulator on Delay and Power of Digital Circuits  Monodeep Kar <sup>1</sup> ; Harish Krishnamurthy <sup>2</sup> ; Sergio Carlo <sup>1</sup> ; Saibal Mukhopadhyay <sup>1</sup> **Georgia Institute of Technology; Intel** | Thermal-Aware Layout Planning for Heterogeneous Datacenters  Reza Azimi; Xin Zhan; Sherief Reda Brown University                                                                                                                                                                                      |  |

| 4:30-4:45 | Break                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                       |  |

| 4:45-6:00 | Session 8A: University Room                                                                                                                                                                                                                                                           | Session 8B: Executive Room                                                                                                                                                                                                                                                                            |  |

|           | Design Contest                                                                                                                                                                                                                                                                        | Poster Presentations                                                                                                                                                                                                                                                                                  |  |

| 6:00 -    | Dinner + Banqu                                                                                                                                                                                                                                                                        | Dinner + Banquet: Birch Aquarium                                                                                                                                                                                                                                                                      |  |

#### ISLPED 2014 Program: Wednesday

|             | Keynote 3: University Room                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                        |

|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 8:30-9:30   | The New (System) Balance of Power and Opportunities for optimizations  Dr. Partha Ranganathan, Google  Session Chairs: Muhammad Khellah (Intel) and Renu Mehra (Synopsys)                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                        |

| 9:30-10:00  | Break                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                        |

| 10:00-11:40 | Session 9A: University Room  Energy Efficient Cache and Memory Design  Session Chairs: Xi Chen (Qualcomm) and Zhenyu Sun (Broadcom)                                                                                                                                                                                                                                  | Session 9B: Executive Room  Energy Harvesting and Energy- Aware System Design  Session Chairs: Naehyuck Chang (Seoul National University) and Hyung Gyu Lee (Daegu University)                                                                                                                                                         |

| 10:00-10:25 | eDRAM-Based Tiered-Reliability Memory with Applications to Low-Power Frame Buffers  Kyungsang Cho <sup>1,2</sup> ; Yongjun Lee <sup>1,2</sup> ; Younghwan Oh <sup>2</sup> ; Gyoo- cheol Hwang <sup>1</sup> ; Jae W. Lee <sup>2</sup> <sup>1</sup> Samsung Electronics; <sup>2</sup> Sungkyunkwan University                                                          | (Best Paper) Fast Photovoltaic Array<br>Reconfiguration for Partial Solar<br>Powered Vehicles  Jaemin Kim <sup>1</sup> ; Yanzhi Wang <sup>2</sup> ;<br>Massoud Pedram <sup>2</sup> ; Naehyuck Chang <sup>1</sup> <sup>1</sup> Seoul National University; <sup>2</sup> USC;                                                             |

| 10:25-10:50 | Enabling High-Performance LPDDRx-Compatible MRAM  Jue Wang <sup>1;</sup> Xiangyu Dong <sup>2</sup> ; Yuan Xie <sup>1</sup> <sup>1</sup> Pennsylvania State University; <sup>2</sup> Qualcomm Technology, Inc.                                                                                                                                                        | Energy Harvesting from Anti-<br>Corrosion Power Sources  Minseok Lee <sup>1</sup> ; Kyeongsu Park <sup>1</sup> ; Sehwan Kim <sup>1</sup> ; Pai Chou <sup>2</sup> <sup>1</sup> Dankook University; <sup>2</sup> University of California, Irvine                                                                                        |

| 10:50-11:15 | SBAC: A Statistics based Cache Bypassing Method for Asymmetric-access Caches  Chao Zhang <sup>1</sup> ; Guangyu Sun <sup>1</sup> ; Peng Li <sup>2</sup> ; Tao Wang <sup>1</sup> ; Dimin Niu <sup>3</sup> ; Yiran Chen <sup>4</sup> <sup>1</sup> Peking University; <sup>2</sup> UCLA; <sup>3</sup> Samsung Semiconductor Inc.; <sup>4</sup> University of Pittsburgh | Intelligent Frame Refresh for Energy-Aware Display Subsystems in Mobile Devices  Yongbing Huang <sup>1,2</sup> ; Mingyu Chen <sup>1</sup> ; Lixin Zhang <sup>1</sup> ; Shihai Xiao <sup>2</sup> ; Junfeng Zhao <sup>2</sup> ; Zhulin Wei <sup>2</sup> ; <sup>1</sup> Chinese Academy of Sciences; <sup>2</sup> Huawei Technologies Co. |

#### ISLPED 2014 Program: Wednesday

| 11:15-11:40 | Tag Check Elision  Zhong Zheng <sup>1</sup> ; Zhiying Wang <sup>1</sup> ; Mikko Lipasti <sup>2</sup> <sup>1</sup> National University of Defense Technology; <sup>2</sup> University of Wisconsin, Madison | (Invited paper) Powering the Internet of Things  Hrishikesh Jayakumar, Kangwoo Lee, Woosuk Lee, Arnab Raha, Younghyun Kim, and Vijay Raghunathan Purdue University |

|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 11:40-12:00 | Break                                                                                                                                                                                                      |                                                                                                                                                                    |

#### **Poster Papers**

QPR.JS: A Runtime Framework for QoS-Aware Power Optimization for Parallel JavaScript Programs

Wonjun Lee<sup>1,2</sup>; Channoh Kim<sup>2</sup>; Houp Song<sup>1</sup>; Jae W. Lee<sup>2</sup>; <sup>1</sup>Samsung Electronics; <sup>2</sup>Sungkyunkwan University

**Ultra-Low Voltage Mixed TFET-MOSFET 8T SRAM Cell**

Yin-Nien Chen; Ming-Long Fan; Pi-Ho Hu; Pin Su; Ching-Te Chuang National Chiao-Tunq University

A-SAD: Power Efficient SAD Calculator for Real time H.264 Video Encoder Using MSB-Approximation Technique

Le Dinh Trang Dang; Ik Joon Chang; Jinsang Kim Kyung Hee University

**Design Exploration of Racetrack Lower-level Caches**

Zhenyu Sun<sup>1</sup>; Xiuyuan Bi<sup>2</sup>; Alex K. Jones<sup>2</sup>; Hai Li<sup>2</sup>

<sup>1</sup>Broadcom Corp.; <sup>2</sup>University of Pittsburgh

A Compact Macromodel for the Charge Phase of a Battery with Typical Charging Protocol

Donghwa Shin<sup>1</sup>; Alessandro Sassone<sup>2</sup>; Alberto Bocca<sup>2</sup>; Alberto Macii<sup>2</sup>; Enrico Macii<sup>2</sup>; Massimo Poncino<sup>2</sup>

<sup>1</sup>Yeungnam University; <sup>2</sup>Politecnico di Torino

**Energy Efficient Task Scheduling on a Multi-core Platform using Real-time Energy Measurements**

Digvijay Singh; William Kaiser University of California, Los Angeles

**Energy-Efficient Mapping of Biomedical Applications on Domain-Specific Accelerator under Process Variation**

Mohammad Khavari Tavana<sup>1</sup>; Amey Kulkarni<sup>2</sup>; Abbas Rahimi<sup>3</sup>; Tinoosh Mohsenin<sup>2</sup>; Houman Homayoun<sup>1</sup>

<sup>1</sup>George Mason University; <sup>2</sup>University of Maryland, Baltimore; <sup>3</sup>University of California, San Diego;

A Memory Rename Table to Reduce Energy and Improve Performance

Joseph Pusdesris; Benjamin VanderSloot; Trevor Mudge University of Michigan A Deterministic-Dither-Based, All-Digital System for On-Chip Power Supply Noise Measurement

Kannan Sankaragomathi; William Smith; Brian Otis; Visvesh Sathe University of Washington

An Open-Source Framework for the Formal Specification and Simulation of Electrical Energy Systems

Sara Vinco<sup>1</sup>; Alessandro Sassone<sup>1</sup>; Franco Fummi<sup>2</sup>; Enrico Macii<sup>1</sup>; Massimo Poncino<sup>1</sup>

<sup>1</sup>Politecnico di Torino; <sup>2</sup>Universita' di Verona

Analysis and Optimization of In-Situ Error Detection Techniques in Ultra-Low-Voltage Pipeline

Seongjong Kim; Mingoo Seok *Columbia University*

Quantifying the Impact of Variability on the Energy Efficiency for a Next-Generation Ultra-Green Supercomputer

Francesco Fraternali<sup>1</sup>; Andrea Bartolini<sup>1</sup>; Carlo Cavazzoni<sup>2</sup>; Giampietro Tecchiolli<sup>3</sup>; Luca Benini<sup>1</sup>

<sup>1</sup>University of Bologna; <sup>2</sup>Cineca; <sup>3</sup>Eurotech Group;

MIN: A Power Efficient Mechanism to Mitigate the Impact of Process Variations on Nanophotonic Networks

Majed Valad Beigi; Gokhan Memik Northwestern university

**EECache: Exploiting Design Choices in Energy-Efficient Last-Level Caches for Chip Multiprocessors**

Hsiang-Yun Cheng; Matthew Poremba; Narges Shahidi ; Ivan Stalev; Mary Jane Irwin; Mahmut Kandemir; John Sampson; Yuan Xie Pennsylvania State University

A Digital Dynamic Write Margin Sensor for Low Power Read/Write Operations in 28nm SRAM

Peter Beshay<sup>1</sup>; Vikas Chandra<sup>2</sup>; Rob Aitken<sup>2</sup>; Benton Calhoun<sup>1</sup> <sup>1</sup>University of Virginia; <sup>2</sup>ARM;

Smart Butterfly: Reducing Static Power Dissipation of Network-on-Chip with Core-State-Awareness

Siyu Yue; Lizhong Chen; Di Zhu; Timothy Pinkston; Massoud Pedram *University of Southern California*

#### **Energy-Efficient Dot Product Computing using a Switched Analog Circuit Architecture**

Ihab Nahlus<sup>1</sup>; Eric Kim<sup>1</sup>; Naresh Shanbhag<sup>1</sup>; David Blaauw<sup>2</sup>

<sup>1</sup>University Of Illinois Urbana Champaign; <sup>2</sup>University Of Michigan Ann-Arbor)

**Gated low-Power Clock Tree Synthesis for 3D-ICs**

Tiantao Lu; Ankur Srivastava University of Maryland

Unlocking the True Potential of 3D CPUs with Micro-Fluidic Cooling

Caleb Serafy; Ankur Srivastava; Donald Yeung University of Maryland, College Park

Prolonging PCM Lifetime through Energy-Efficient, Segment-Aware, and Wear-Resistant Page Allocation

Hoda Aghaei Khouzani; Yuan Xue; Archana Pandurangi; Chengmo Yang University of Delaware

#### **Maps: Sheraton La Jolla Hotel**

# **Maps: Birch Aquarium from the Hotel**

#### Sponsored by:

#### **Technical support by:**

#### **Industry Gold Sponsors**

#### **Industry Silver Sponsors**

#### **Industry Bronze Sponsors**